Digilent Nexys2 Referenzhandbuch - Seite 13

Blättern Sie online oder laden Sie pdf Referenzhandbuch für Hauptplatine Digilent Nexys2 herunter. Digilent Nexys2 18 Seiten.

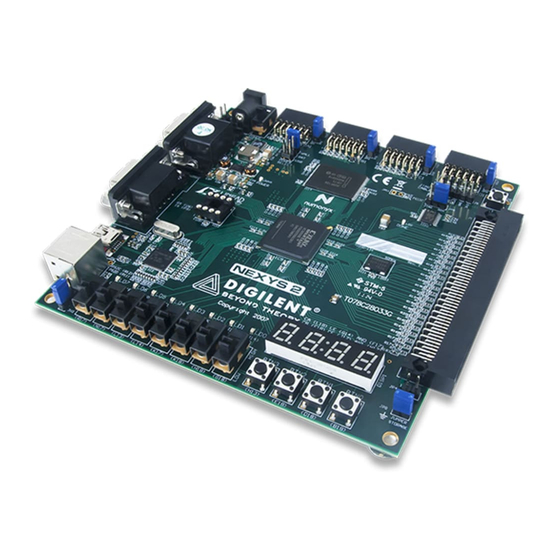

Nexys2 Reference Manual

Serial Port

The Nexys2 contains a two-wire serial port based on an ST Microelectronics ST3232 voltage

converter. The ST3232 converts the signal levels used by RS-232 communications (-12 to -3 for a

logic '1' and 12V to 3V for a logic '0') to the 3.3V signals used by the FPGA. Since only two signals

are connected (RXD and TXD), an FPGA-based serial port controller can only use software hand-

shaking protocols (XON/XOFF). The Nexys2 serial port is useful for many applications, and in

particular for debugging and working with Xilinx's MicroBlaze embedded processor.

The two devices connected to either end of a serial cable are known as the Data Terminal Equipment

(DTE) and the Data Communications Equipment (DCE). The DCE was originally conceived to be a

modem, but now many devices connect to a computer as a DCE. A DTE "source" device uses a male

DB-9 connector, and a DCE

"peripheral" device uses a female

DB-9 connector. Two DTE devices

can be connected via a serial

cable only if lines two and three

(RXD and TXD) are crossed,

producing what is known as a null

modem cable. A DTE and DCE

device can be connected with a

straight-through cable. The

Nexys2 is configured as a DCE

device, with the assumption it will

most typically be connected to a

DTE device like a computer.

Memory

The Nexys2 board has external RAM and ROM devices. The external RAM is a 128Mbit Micron

M45W8MW16 Cellular RAM pseudo-static DRAM device organized as 8Mbytes x 16bits. It can

operate as a typical asynchronous SRAM with read and write cycle times of 70ns, or as a

synchronous memory with an 80MHz bus. When operated as an asynchronous SRAM, the Cellular

RAM automatically refreshes its internal DRAM arrays, allowing for a simplified memory controller

design (similar to any SRAM) in the FPGA. When operated in synchronous mode, continuous

transfers of up to 80MHz are possible.

The external ROM is a 128Mbit Intel TE28F128J3D75-110 StrataFlash device organized as 8Mbytes

x 16bits. Internally, it contains 128 blocks that can be individually erased, and it supports 110ns read

cycle times, with 25ns page-mode reads within blocks. It has an internal 32-byte write buffer that can

be written with 70ns cycle times, and the 32-byte buffer can be transferred to the Flash array in 218us

(typical).

Both devices share a common 16-bit data bus and 24-bit address bus. The Cellular RAM is byte

addressable using the upper-byte and lower-byte signals (MT-UB and MT-LB), but the StrataFlash is

configured for 16 byte operations only (it is not byte addressable). The output enable (OE) and write

enable (WE) signals are shared by both devices, but each device has individual chip enable (CE)

signals. Additionally, the Cellular RAM has clock (MT-CLK), wait (MT-WAIT), address valid (MT-ADV)

and control register enable (MT_CRE) signals available to the FPGA for use with synchronous

transfers, and the StrataFlash has Reset (RP#) and status (STS) signals routed to the FPGA.

Copyright Digilent, Inc.

P9

U6

100

Spartan 3E

FPGA

Figure 21: Nexys2 serial port circuit

Page 13/17

T1IN

T1OUT

R1OUT

R1IN

ST3232

RS-232

voltage

converter

Digilent

www.digilentinc.com

DB-9

1

DCD

2

RXD

3

TXD

4

DTR

5

SG

6

DSR

7

RTS

8

CTS

9

RI

Doc: 502-134