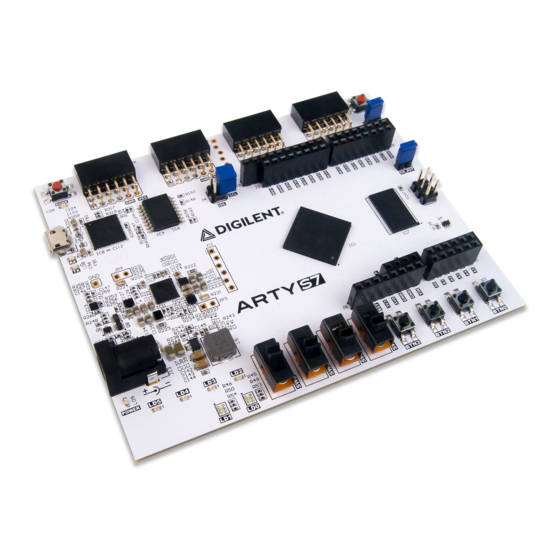

Digilent Arty S7 Manuel de référence - Page 12

Parcourez en ligne ou téléchargez le pdf Manuel de référence pour {nom_de_la_catégorie} Digilent Arty S7. Digilent Arty S7 14 pages.

Pin Name

Shield Function

SDA

I2C Data

IO13

General purpose I/O,

SPI Clock

IO11

General purpose I/O,

SPI Data out

IO12

General purpose I/O,

SPI Data in

IO10

General purpose I/O,

SPI Slave Select

A0-A5

Single-Ended Analog

Input

A6-A9

Differential Analog

Input

V_P, V_N

Dedicated Differential

Analog Input

XGND

XADC Analog Ground

XVREF

XADC Analog Voltage

Reference

Not Connected

N / C

IOREF

Digital I/O Voltage

reference

RST

Reset to Shield

3V3

3.3V Power Rail

5V0

5.0V Power Rail

GND (), G

Ground

VIN

Power Input

Table 9.1. Arty S7 Shield Pinout

9.1 Shield Digital I/O

The pins connected directly to the FPGA can be used as general purpose inputs or outputs. These pins include the I2C, SPI, and general purpose I/O pins. There are 200 Ohm series

resistors between the FPGA and the digital I/O pins to help provide protection against accidental short circuits (pins A10 and A11 instead have 140 Ohm series resistors). The

absolute maximum and recommended operating voltages for these pins are outlined in Table 9.1.1.

Absolute Minimum

Voltage

Powered

-0.4 V

Unpowered

-0.4 V

Table 9.1.1. Shield Voltage Specifications

For more information on the electrical characteristics of the pins connected to the FPGA, please see the

(https://www.xilinx.com/support/documentation/data_sheets/ds189-spartan-7-data-sheet.pdf)

The pins on the shield connector typically used for I2C signals are labeled as SCL and SDA. When using these signals to implement an I2C bus it is necessary to attach a pull-up

resistor to them. On the Arty S7, this can be done by placing two shorting blocks horizontally across the J4 header.

9.2 Shield Analog I/O

The pins labeled A0-A9 and V_P/V_N are used as analog inputs to the XADC module of the FPGA. The FPGA expects that the inputs range from 0-1 V. On the pins labeled A0-A5

we use an external circuit to scale down the input voltage from 3.3V. This circuit is shown in Figure 9.2.1. This circuit allows the XADC module to accurately measure any voltage

between 0V and 3.3V (relative to the Arty S7's GND ()) that is applied to any of these pins. If you wish to use the pins labeled A0-A5 as Digital inputs or outputs, they are also

connected directly to the FPGA before the resistor divider circuit (also shown in Figure 9.2.1).

Arty S7 Connection

See Section titled "Shield Digital I/O"

See Section titled "Shield Digital I/O"

See Section titled "Shield Digital I/O"

See Section titled "Shield Digital I/O"

See Section titled "Shield Digital I/O"

See Section titled "Shield Analog I/O"

See Section titled "Shield Analog I/O"

See Section titled "Shield Analog I/O"

Connected to net used to drive the XADC ground reference on the FPGA (VREFN)

Connected to 1.25 V, 25mA rail used to drive the XADC voltage reference on the FPGA (VREFP)

Not Connected

Connected to the Arty S7 3.3V Power Rail (See the "Power Supplies" section)

Connected to the red "RESET" button and a Digital I/O of the FPGA. When JP2 is shorted, it is also

connected to the DTR signal of the FTDI USB-UART bridge.

Connected to the Arty S7 3.3V Power Rail (See the "Power Supplies" section)

Connected to the Arty S7 5.0V Power Rail (See the "Power Supplies" section)

Connected to the Ground plane of Arty S7

Connected in parallel with the external power supply connector (J12). See the "Power Supplies" section for

information on powering the Arty S7 from this pin.

Recommended Minimum Operating

Voltage

-0.2 V

N/A

Recommended Maximum Operating

Voltage

3.4 V

N/A

Spartan-7 datasheet

from Xilinx.

Shared

Connections

–

SCLK () pin of SPI

Connector

MOSI () pin of SPI

Connector

MISO () pin of SPI

Connector

SS pin of SPI

Connector

–

–

–

–

–

–

–

–

–

–

–

–

Absolute Maximum

Voltage

3.75 V

0.55 V