- ページ 10

マザーボード Digilent PLTW S7のPDF リファレンス・マニュアルをオンラインで閲覧またはダウンロードできます。Digilent PLTW S7 11 ページ。

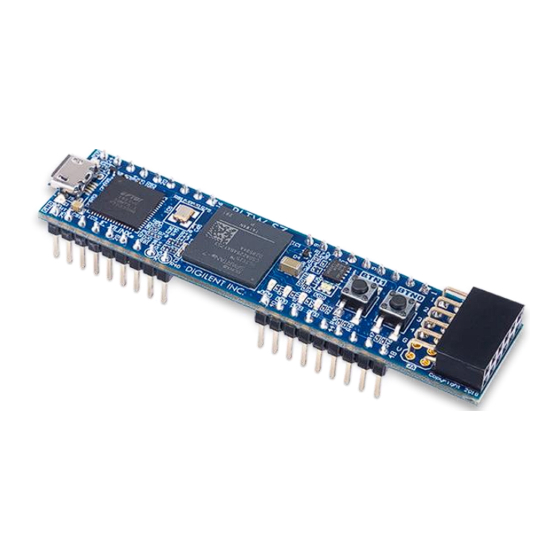

PLTW S7 Reference Manual

any voltage between 0V and 3.3V (relative to GND on pin 25) that is applied to these pins. The analog inputs can

tolerate input voltages of up to 5.5V, though any voltage above 3.3V will be read as 3.3V by the XADC module.

The XADC core within the Spartan-7 is a dual-channel 12-bit analog-to-digital converter capable of operating at 1

MSPS. Either channel can be driven by either of the two auxiliary analog inputs to the DIP pins. The XADC core is

controlled and accessed from a user design via the Dynamic Reconfiguration port (DRP). The DRP also provides

access to a temperature sensor that is internal to the FPGA. For more information on using the XADC core, refer

to

Xilinx

UG480, titled "7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-

Digital Converter". A demo that uses the XADC core is available on the

8

Pmod Connector

Pmod connectors are 2×6, right-angle, 100-mil spaced female connectors that mate with standard 2×6 pin

headers. Each 12-pin Pmod connector provides two 3.3V VCC signals (pins 6 and 12), two Ground signals (pins 5

and 11), and eight logic signals, as sown in Figure 8.1. The VCC and Ground pins can deliver up to 200mA of

current, but care must be taken not to exceed any of the power budgets of the onboard regulator or the external

power supply (described in the Power Supplies section).

Digilent provides a large collection of Pmod accessory boards that can attach to Pmod expansion connectors to

add ready-made functions like A/D's, D/A's, motor drivers, sensors, and other functions.

See

www.digilentinc.com

for more information.

The PLTW S7 has one "standard" type Pmod connector, and the FPGA pin connections for it are described in Table

8.1. Standard Pmod connectors are connected to the FPGA via 200 Ohm series resistors. The series resistors

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Figure 7.2.1 Analog Input Circuit.

PLTW S7 Resource

Figure 8.1. Pmod Diagram.

Center.

Page 10 of 11