Digilent PLTW S7 참조 매뉴얼 - 페이지 4

{카테고리_이름} Digilent PLTW S7에 대한 참조 매뉴얼을 온라인으로 검색하거나 PDF를 다운로드하세요. Digilent PLTW S7 11 페이지.

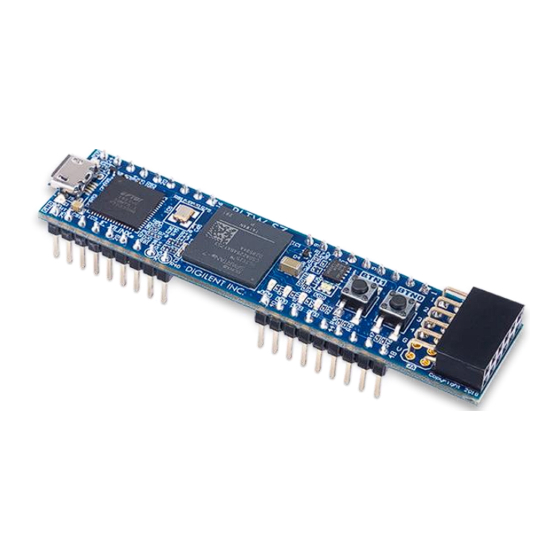

PLTW S7 Reference Manual

2

FPGA Configuration

After power-on, the Spartan-7 FPGA must be configured (or programmed) before it can perform any functions. The

FPGA can be configured in one of two ways:

•

A PC can use the Digilent USB-JTAG circuitry (port J5) to program the FPGA any time the power is on.

•

A file stored in the nonvolatile serial (SPI) flash device can be transferred to the FPGA using the SPI port.

Figure 2.1 shows the different options available for configuring the FPGA.

The FPGA configuration data is stored in files called bitstreams that have the .bit file extension. The Vivado

software from Xilinx can create bitstreams from VHDL, Verilog®, or block-level designs.

Bitstreams are stored in volatile memory cells within the FPGA. This data defines the FPGA's logic functions and

circuit connections, and it remains valid until it is erased by removing board power, or by writing a new

configuration file using the JTAG port.

A Spartan-7 25T bitstream is typically 9,935,224 bits. The time it takes to program the PLTW S7 can be decreased

by compressing the bitstream before programming, and then allowing the FPGA to decompress the bitstream itself

during configuration. Depending on design complexity, compression ratios of 10x can be achieved. Bitstream

compression can be enabled within the Xilinx tools to occur during generation and is enabled by default in the

PLTW S7's master XDC file. For more information on how to do this, consult the Xilinx documentation for the

toolset being used.

After successful programming, the FPGA will cause the "DONE" LED to illuminate.

The following sections provide greater detail about programming the PLTW S7 using the different methods

available.

2.1

JTAG Configuration

The Xilinx tools typically communicate with FPGAs using the Test Access Port and Boundary-Scan Architecture,

commonly referred to as JTAG. During JTAG programming, a .bit file is transferred from the PC to the FPGA using

the onboard Digilent USB-JTAG circuitry (port J5). JTAG programming can be performed any time after the PLTW S7

has been powered on. If the FPGA is already configured, then the existing configuration is overwritten with the

bitstream being transferred over JTAG.

Programming the PLTW S7 with an uncompressed bitstream using the onboard USB-JTAG circuitry usually takes

around 2 seconds. JTAG programming can be performed by Vivado's Hardware Manager.

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Figure 2.1. Configuration.

Page 4 of 11