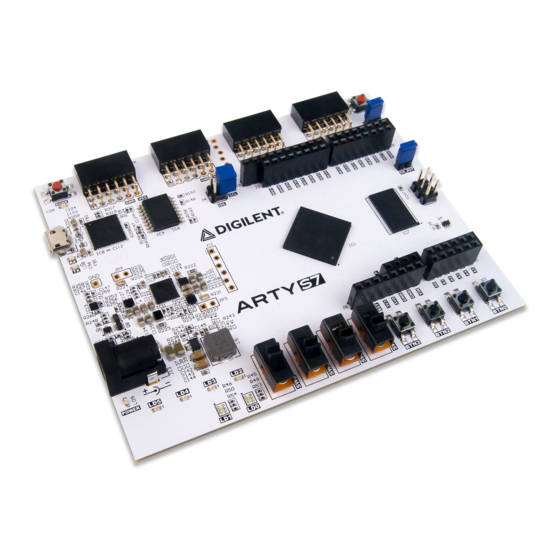

Digilent Arty S7 Справочное руководство - Страница 7

Просмотреть онлайн или скачать pdf Справочное руководство для Материнская плата Digilent Arty S7. Digilent Arty S7 14 страниц.

(https://reference.digilentinc.com/_detail/arty/arty_rm_power-02.png?id=reference%3Aprogrammable-logic%3Aarty-s7%3Areference-manual)

Voltage regulator circuits from Analog Devices and Texas Instruments create the required 3.3V, 1.8V, 1.35V, 1.25V, and 1.00V supplies from the 5V power source. In the event that an

external supply or battery pack is used, the on-board Analog Devices 5V regulator provides the 5V source. Table 1.1 provides additional information (typical currents depend strongly

on FPGA configuration and the values provided are typical of medium size/speed designs).

Supply

Circuits

5V

Onboard Regulators, RGB LEDs

3.3V

FPGA I/O, Clocks, Flash, PMODs, LEDs, Buttons, Switches, USB port

1.00V

FPGA Core and Block RAM ()

1.8V

FPGA Auxiliary

1.35V

DDR3L and associated FPGA bank

1.25V

XADC Analog Reference

Table 1.1. Arty S7 Power Rails.

1.1 Current Monitoring

The 1.0V and 1.8V rails each have a 0.010 Ohm current sense resistor for monitoring the amount of current being consumed by them. You can access them via JP3 for the 1.0V rail

and JP4 for the 1.8V rail. To calculate the current on each power rail, use Ohm's law with R=0.010 and V equal to the measured voltage across the jumper. To measure the voltage you

can use an external digital multimeter or oscilloscope.

2 FPGA Configuration

After power-on, the Spartan-7 FPGA must be configured (or programmed) before it can perform any functions. You can configure the FPGA in one of two ways:

1. A PC can use the Digilent USB-JTAG circuitry (port J10) to program the FPGA any time the power is on.

2. A file stored in the nonvolatile serial (SPI) flash device can be transferred to the FPGA using the SPI port.

(https://reference.digilentinc.com/_detail/reference/programmable-logic/arty-s7/arty-s7-config.png?id=reference%3Aprogrammable-logic%3Aarty-s7%3Areference-manual)

Configuration.

Figure 2.1 shows the different options available for configuring the FPGA. An on-board "mode" jumper (JP1) selects whether the FPGA will be programmed by the Quad-SPI flash

on power up.

The FPGA configuration data is stored in files called bitstreams that have the .bit file extension. The Vivado software from Xilinx can create bitstreams from VHDL, Verilog®, or

block-level design.

Bitstreams are stored in volatile memory cells within the FPGA. This data defines the FPGA's logic functions and circuit connections, and it remains valid until it is erased by removing

board power, by pressing the reset button attached to the PROG input, or by writing a new configuration file using the JTAG port.

A Spartan-7 50T bitstream is typically 17,536,096 bits. The time it takes to program the Arty S7 can be decreased by compressing the bitstream before programming, and then allowing

the FPGA to decompress the bitstream itself during configuration. Depending on design complexity, compression ratios of 10x can be achieved. Bitstream compression can be enabled

within the Xilinx tools to occur during generation. For instructions on how to do this, consult the Xilinx documentation for the toolset being used.

After being successfully programmed, the FPGA will cause the "DONE" LED () to illuminate. Pressing the "PROG" button at any time will reset the configuration memory in the

FPGA. After being reset, if JP1 is set then the FPGA will immediately attempt to reprogram itself from Quad SPI flash.

The following sections provide greater detail about programming the Arty S7 using the different methods available.

2.1 JTAG Configuration

The Xilinx tools typically communicate with FPGAs using the Test Access Port and Boundary-Scan Architecture, commonly referred to as JTAG. During JTAG programming, a .bit

file is transferred from the PC to the FPGA using the onboard Digilent USB-JTAG circuitry (port J10) or an external JTAG programmer, such as the Digilent JTAG-HS2, attached to

port J9. You can perform JTAG programming any time after the Arty S7 has been powered on, regardless of whether the mode jumper (JP1) is set. If the FPGA is already configured,

then the existing configuration is overwritten with the bitstream being transmitted over JTAG. Not setting the mode jumper (seen in Figure 2.1) is useful to prevent the FPGA from

being configured from Quad-SPI Flash until a JTAG programming occurs.

Programming the Arty S7 with an uncompressed bitstream using the on-board USB-JTAG circuitry usually takes around 6 seconds. JTAG programming can be done using the

hardware manager in Vivado.

Figure 1.2. Arty S7 Battery Pack Connection.

Device

IC13: Analog Devices ADP2384

IC12: Analog Devices ADP5052

IC12: Analog Devices ADP5052

IC12: Analog Devices ADP5052

IC12: Analog Devices ADP5052

IC14: Texas Instruments REF3012

Current (max/typical)

3.5A/0.375A to 2A

2.2A/NA

1.0A/0.2A to 0.8A

1.0A/NA

1.0A/NA

25mA/NA

Figure 2.1. Arty S7 FPGA