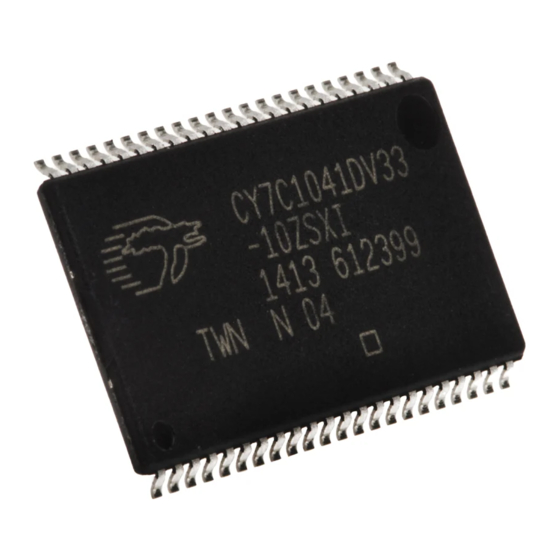

Cypress Semiconductor CY7C1041DV33 사양 시트

{카테고리_이름} Cypress Semiconductor CY7C1041DV33에 대한 사양 시트을 온라인으로 검색하거나 PDF를 다운로드하세요. Cypress Semiconductor CY7C1041DV33 14 페이지. 4 mbit (256k x 16) static ram

Features

■

Pin and function compatible with CY7C1041CV33

■

High speed

❐

t

= 10 ns

AA

■

Low active power

❐

I

= 90 mA at 10 ns (industrial)

CC

■

Low CMOS standby power

❐

I

= 10 mA

SB2

■

2.0V data retention

■

Automatic power down when deselected

■

TTL compatible inputs and outputs

■

Easy memory expansion with CE and OE features

■

Available in Pb-free 48-ball VFBGA, 44-pin (400-mil) molded

SOJ, and 44-pin TSOP II packages

Logic Block Diagram

Note

1. For guidelines on SRAM system design, refer to the "System Design Guidelines" Cypress application note, available at www.cypress.com.

Cypress Semiconductor Corporation

Document #: 38-05473 Rev. *E

INPUT BUFFER

A

0

A

1

A

2

A

3

A

256K × 16

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

•

198 Champion Court

4 Mbit (256K x 16) Static RAM

Functional Description

[1]

The CY7C1041DV33

is a high performance CMOS Static RAM

organized as 256K words by 16 bits. To write to the device, take

Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte

LOW Enable (BLE) is LOW, then data from IO pins (IO

is written into the location specified on the address pins (A

A

). If Byte HIGH Enable (BHE) is LOW, then data from IO pins

17

(IO

to IO

) is written into the location specified on the address

8

15

pins (A

to A

).

0

17

To read from the device, take Chip Enable (CE) and Output

Enable (OE) LOW while forcing the Write Enable (WE) HIGH. If

BLE is LOW, then data from the memory location specified by

the address pins appears on IO

from memory appears on IO

page 9 for a complete description of read and write modes.

The input and output pins (IO

impedance state when the device is deselected (CE HIGH),

outputs are disabled (OE HIGH), BHE and BLE are disabled

(BHE, BLE HIGH), or during a write operation (CE LOW and WE

LOW).

The CY7C1041DV33 is available in a standard 44-pin 400-mil

wide SOJ and 44-pin TSOP II package with center power and

ground (revolutionary) pinout and a 48-ball fine-pitch ball grid

array (FBGA) package.

IO

–IO

0

7

IO

–IO

8

15

BHE

WE

CE

OE

BLE

,

•

San Jose

CA 95134-1709

CY7C1041DV33

to IO

0

to IO

. If BHE is LOW, then data

0

7

to IO

. See the

Truth Table

8

15

to IO

) are placed in a high

0

15

•

408-943-2600

Revised July 17, 2008

)

7

to

0

on

[+] Feedback

[+] Feedback