Digilent PLTW S7 Reference Manual - Page 9

Browse online or download pdf Reference Manual for Motherboard Digilent PLTW S7. Digilent PLTW S7 11 pages.

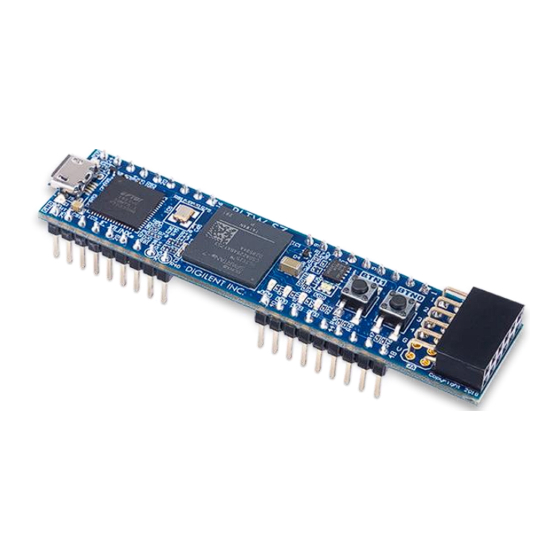

PLTW S7 Reference Manual

VU (pin 24) can be used to power the PLTW S7 when it is not connected to a USB Host. When the device is

connected to a USB host, VU is driven by the 5V rail of the USB connector and can be used to power devices

external to the PLTW S7. See the

7.1

DIP Digital I/O

The pins directly connected to the FPGA can be used as general-purpose inputs or outputs. Each of these pins is

connected to the FPGA via a 620 Ohm series resistor. The series resistors prevent short circuits that can occur if a

user accidentally drives a signal that is supposed to be used as an input. In combination with Schottky diodes

placed between the 3.3V power rail and each digital pin, these resistors also help to protect the FPGA from high

input voltages. The downside to this added protection is that the maximum switching speed of these signals is

limited to 5 MHz. These pins support input voltages of up to 5.5V.

For more information on the electrical characteristics of these pins, please see Xilinx's

7.2

Analog Inputs

Pins 32 and 33 of the DIP headers are used as analog inputs to the XADC module of the FPGA. The FPGA expects

that the inputs range from 0V-1V, so resistor-divider circuits are used on the PLTW S7 to scale down the input

voltage from 3.3V. This circuit is shown in Figure 7.2.1. This circuit allows the XADC module to accurately measure

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Figure 7.1. DIP Pin Diagram.

Power Supplies

section for more information.

Spartan-7

Datasheet.

Page 9 of 11