Avnet AES-LPA-502-G 사용자 설명서 - 페이지 5

{카테고리_이름} Avnet AES-LPA-502-G에 대한 사용자 설명서을 온라인으로 검색하거나 PDF를 다운로드하세요. Avnet AES-LPA-502-G 17 페이지. Differential breakout card for zynq ultrascale+ rfsoc

2 Pin Assignment

The following sections provide information on assignment of signals to pins.

2.1

Digital IO & Power Rails

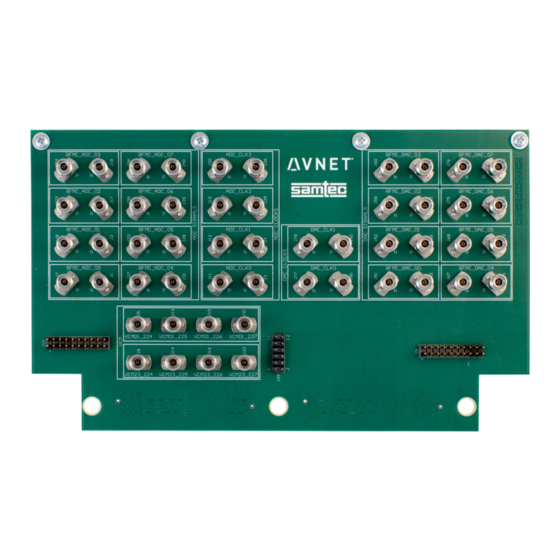

The Xilinx RFMC connector standard provides various digital IO and power rails. The AES-LPA-

502-G provides access to these signals at standard 0.1 mil headers J9, J10 and J29.

The tables below show how the GPIO pins have been assigned.

Differential Breakout card for Zynq UltraScale+ RFSoC – Hardware User's Guide

Figure 2 - Header Pins for RFMC Digital IO Signals

Figure 3 - Header Pins for RFMC I2C and Power Rails

Page 5

Hardware User's Guide